Chapter 1. Hardware Interface Driver

- Table of Contents

- 1.1. External Library Dependencies

- 1.2. Register Model

- 1.2.1. PCI Configuration Space Registers

- 1.2.2. PCI I/O Space Registers

- 1.2.2.1. Control and Status Register (CSR)

- 1.2.2.2. FIFO Faults Register

- 1.2.2.3. EVENTS_BASE and EVENTS_FREE Registers

- 1.2.3. PCI Memory Space Registers

- 1.3. Initialization and Configuration

- 1.3.1. Initialization

- 1.3.1.1. Interface Allocation

- 1.3.1.2. Board Discovery

- 1.3.2. Default Configuration

- 1.3.2.1. PCI Configuration Space Registers

- 1.3.2.2. PCI I/O Space Registers

- 1.4. LCB Statistics

- 1.4.1. Hardware Statistics

- 1.4.2. LATp I/O Statistics

The hardware interface driver supports low-level services of the LCB, including:

Access to the LCB PCI registers.

Initialization and configuration routines.

LCB Statistics.

The hardware interface is intended to be a private interface used by LCBD to support the high-level public interface. However, the hardware engineer designing and implementing the LCB may also find the hardware interface useful for debugging purposes.

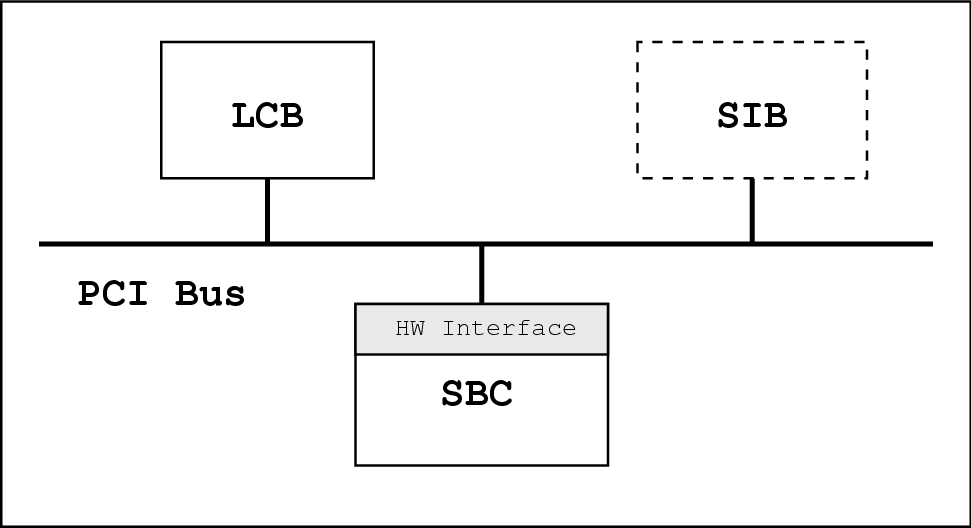

A diagram of the cPCI crate and PCI bus is shown in Figure 1-1. This diagram shows the relationship between the single board computer (SBC), the hardware interface, the PCI bus and the LCB.